## High K Oxides (Design Specifications and Challenge Mitigation)

Eric Brueckner

Literature Seminar

October 16, 2008

Since the introduction of integrated circuits (IC), much research has been focused on scaling feature sizes to ever smaller dimensions. This trend was described in 1965 by Dr. Gordon E. Moore where he predicted the number of transistors per chip to double every eighteen months. Moore's Law, has served as a benchmark for the IC industry, ushering in the newest generation of components at the 45nm node. Complementary Metal Oxide Semiconductor Field Effect Transistors (CMOS FET) have been the primary devices on an IC logic circuit. Utilizing a metal/oxide stack held at a controlled bias on a doped semiconductor substrate, the current between the source and drain can be manipulated, creating an on (I<sub>on</sub>) or off (I<sub>off</sub>) current.

Oxide layers serve as capacitors,3 where capacitance, C, is

$$C = \frac{\varepsilon_0 K A}{d}$$

and  $\epsilon_0$  is permittivity of air, K is the dielectric constant, A is area, and d is oxide thickness. Oxide thickness of CMOS devices went below 2nm, only several atomic layers, thus reaching its physical and practical limitation. Electron tunneling through these thin layers caused an unacceptably high leakage current and called for new materials to control this problem and allow for further scaling.

Grown by thermal oxidation, SiO<sub>2</sub> has driven the semiconductor industry to unimaginable heights due in large part to its supreme interface with Si. High K oxides must be deposited; therefore a lower quality interface is expected. Atomic layer deposition<sup>2,5-7</sup> has shown to exhibit sub-monolayer control of film thickness,<sup>8</sup> however the presence of excess oxygen has led to oxidation of the Si subsurface increasing the effective oxide thickness (EOT) of the dielectric layer.<sup>9</sup>

$$EOT = \frac{K_{SiO2}}{K_{HighK}} d_{HighK} = \frac{3.9}{K_{HighK}} d_{HighK}$$

Moreover, grain boundaries promote diffusion of O and Si but cannot be easily avoided due to the low crystallization temperature of many high K oxides. Silicate and silicon dioxide interlayers will ultimately limit scalability. Therefore, an abrupt high K oxide/Si interface is required to achieve the lowest EOT.

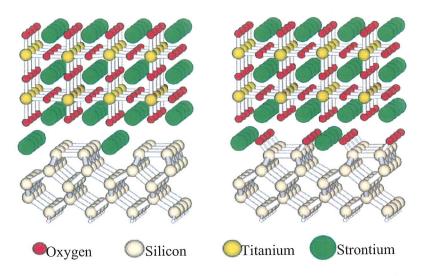

Choice of high K oxides has proven to be a difficult task, where parameters such as thermodynamic and kinetic stability, band offset, structural defects, etc, must be controlled.<sup>2,4</sup> Of paramount importance is the interface between silicon and the high K oxide. Controlling the Si/high K oxide interface will ensure minimal electronic defects serving as traps to charge carriers. Först, et al<sup>4</sup> performed a theoretical study of the interface between Si and SrTiO<sub>3</sub>. Owing to the presence of dangling bonds<sup>11</sup> on a clean Si(001) surface, a ½ monolayer of Sr is first required to passivate the surface thereby removing any surface states in the band gap. Using this surface as a suitable building block for oxide layer formation, layers of SrO or SrTiO<sub>3</sub> can be deposited. An annealing cycle of 600K crystallizes the structure, forming an atomically abrupt interface. The

effects of oxidation were found to attack the empty Si coordination site. All coordination sites are occupied after addition of a full monolayer of O atoms.

Figure 1: Si(001)/SrTiO<sub>3</sub> atomic structure, Sr passivated (left) and oxidized (right)

Park et al<sup>7</sup> have sputtered a thin (0.5nm) film of Hf on a HfO<sub>2</sub>(5nm)/Si surface in attempt to suppress Si diffusion into the HfO<sub>2</sub> layer forming Hf-silicate. Owing to fewer nucleation sites under the top Hf metal layer, larger grain sizes were observed by high resolution transmission electron microscopy thereby reducing the grain boundary density. Similarly, Kobayashi et al<sup>9</sup> have deposited a thin (1nm) SiN layer followed by a 3nm HfO<sub>2</sub> layer to prevent diffusion of Hf and O and the subsequent interface reactions. EOT of the SiN-containing samples remain constant after a post-deposition anneal and show a lower leakage current density compared to that of the as-deposited SiN-containing samples.

## References

- 1. Moore, G. "Cramming more Components onto Integrated Circuits" *Electronics* **1965**, 38, 8

- 2. Tapily, K.; Jakes, J.E.; Stone, D.S.; Shrestha, P.; Gu, D.; Baumgart, H.; Elmustafa, A.A. "Nanoindentation Investigation of HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> Films Grown by Atomic Layer Deposition" *Journal of The Electrochemical Society* **2008**, 155(7), H545-H551

- 3. Robertson, J. "High Dielectric Constant Oxides" Eur. Phys. J. Appl. Phys. 2004, 28, 265-291

- 4. Först, C.J.; Ashman, C.R.; Schwarz, K.; Blöch, P.E. "The Interface Between Silicon and a High-k Oxide" *Nature* **2004**, 427, 53-56

- 5. Knez, M.; Nielsch, K.; Niinistö, L. "Synthesis and Surface Engineering of Complex Nanostructures by Atomic Layer Deposition" *Adv. Mater.* **2007**, 19, 3245-3438

- 6. Damlencourt, J.-F.; Renault, O.; Samour, D.; Papon, A.-M.; Leroux, C.; Martin, F.; Marthon, S.; Séméria, M.-N.; Garros, X. "Electrical and Physico-chemical Characterization of HfO<sub>2</sub>/SiO<sub>2</sub> Gate Oxide Stacks Prepared by Atomic Layer Deposition" *Solid-State Electronics* **2003**, 1613-1616

- 7. Park, T.J.; Kim, J.H.; Jang, J.H.; Seo, M.; Na, K.D.; Hwang, C.S. "Enhancement in Thermal Stability of Atomic Layer Deposited HfO<sub>2</sub> Films by using Top Hf Metal Layer" *Microelectronic Engineering* **2007**, 2226-2229

- 8. Lee, D.; Seidel, T.; Dalton, J.; Liu, T.K. "ALD Refill of Nanometer-Scale Gaps with High-κ Dielectric for Advanced CMOS Technologies" *Electrochemical and Solid-State Letters* **2007**, 10(9), H257-H259

- 9. Robertson, J. "Interfaces and Defects of High-K Oxides on Silicon" *Solid-State Electronics* **2005**, 49, 283-293

- 10. Van Elshocht, S.; Adelmann, C.; Conrad, T.; Delabie, A.; Franquet, A.; Nyns, L.; Richard, O.; Lehnen, P.; Swerts, J.; De Gendt, S. "Silicate Formation and Thermal Stability of Ternary Rare Earth Oxides as High-k Dielectrics" *J. Vac. Sci. Technol. A* **2008**, 26(4), 724-730

- 11. Robertson, J.; Peacock, P.W. "Bonding and Structure of some High-k Oxide: Si Interfaces" *Phys. Stat. Sol. (B)* **2004**, 241, 10, 2236-2245

- 12. Kobayashi, H.; Imamura, K.; Fukayama, K.; Im, S.-S.; Maida, O.; Kim, Y.-B.; Kim, H.-C.; Choi, D.-K. "Complete Prevention of Reaction at HfO<sub>2</sub>/Si Interfaces by 1 nm Silicon Nitride Layer" *Surface Science* **2008**, 602, 1948-1953